# **Solutions - Midterm Exam**

(February 14th @ 5:30 pm)

Presentation and clarity are very important! Show your procedure!

# **PROBLEM 1 (22 PTS)**

a) Complete the following table. The decimal numbers are unsigned: (3 pts.)

| Decimal | BCD          | Binary   | Reflective Gray Code |

|---------|--------------|----------|----------------------|

| 50      | 01010000     | 110010   | 101011               |

| 128     | 000100101000 | 10000000 | 11000000             |

b) Complete the following table. The decimal numbers are signed. Use the fewest number of bits in each case: (15 pts.)

| REPRESENTATION |                    |                |                |  |

|----------------|--------------------|----------------|----------------|--|

| Decimal        | Sign-and-magnitude | 1's complement | 2's complement |  |

| -17            | 110001             | 101110         | 101111         |  |

| -16            | <b>1</b> 10000     | 101111         | 10000          |  |

| -32            | 1100000            | 1011111        | 100000         |  |

| -1             | 11                 | 10             | 1111           |  |

| 41             | 0101001            | 0101001        | 0101001        |  |

| 0              | 10                 | 1111           | 0              |  |

c) Convert the following decimal numbers to their 2's complement representations. (4 pts)

```

-17.25 \checkmark 16.75 +17.25 = 010001.01 <math>\Rightarrow -17.25 = 101110.11 +16.75 = 010000.11

```

#### PROBLEM 2 (15 PTS)

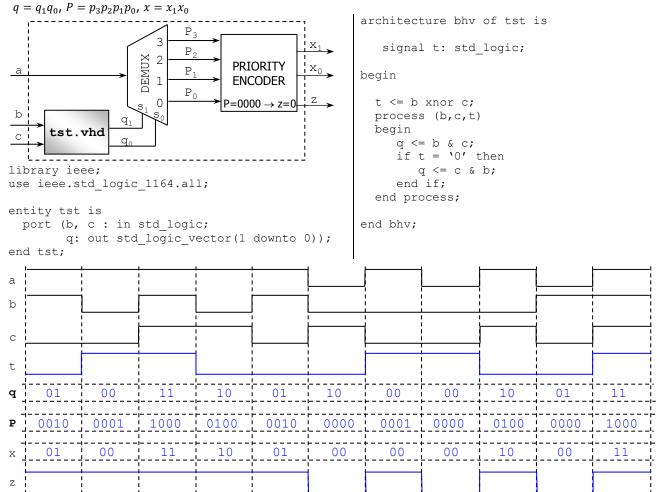

Complete the timing diagram of the following circuit. The VHDL code (tst.vhd) corresponds to the shaded circuit.

1

# **PROBLEM 3 (12 PTS)**

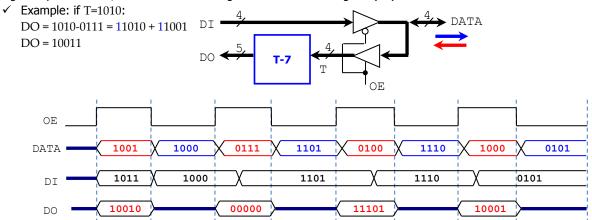

• Complete the timing diagram (signals *DO* and *DATA*) of the following circuit. The circuit in the blue box computes the signed operation T-7, with the result having 5 bits. T is a 4-bit signed (2C) number.

#### PROBLEM 4 (10 PTS)

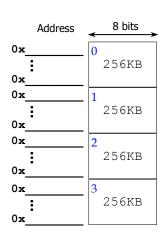

- A microprocessor has a memory space of 1 MB. Each memory address occupies one byte.  $1KB = 2^{10}$  bytes,  $1MB = 2^{20}$  bytes,  $1GB = 2^{30}$  bytes.

- a) What is the address bus size (number of bits of the address) of the microprocessor? Size of memory space:  $1 \text{ MB} = 2^{20}$  bytes. Thus, we require 20 bits to address the memory space.

- b) What is the range (lowest to highest, in hexadecimal) of the memory space for this microprocessor? (1 pt.) With 20 bits, the address range is 0x00000 to 0xFFFFFF.

- c) The figure to the right shows four memory chips that are placed in the given positions:

✓ Complete the address ranges (lowest to highest, in hexadecimal) for each of the memory chips. (8 pts)

| •            |          |      |      |                | Address            | _ | 8 bits |

|--------------|----------|------|------|----------------|--------------------|---|--------|

| 0000         | 0000     | 0000 | 0000 | 0000:<br>0001: | 0x00000<br>0x00001 | 0 | 256KB  |

| 0011         | <br>1111 | 1111 | 1111 | 1111:          | 0x3FFFF            |   |        |

| 0100<br>0100 | 0000     | 0000 | 0000 | 0000:<br>0001: | 0x40000<br>0x40001 | 1 | 256KB  |

| 0111         | 1111     | 1111 | 1111 | 1111:          | 0x7FFFF            |   |        |

| 1000<br>1000 | 0000     | 0000 | 0000 | 0000:          | 0x80000<br>0x80001 | 2 | 256KB  |

| 1011         | <br>1111 | 1111 | 1111 | 1111:          | 0xBFFFF            |   |        |

| 1100<br>1100 | 0000     | 0000 | 0000 | 0000:<br>0001: | 0xC0000<br>0xC0001 | 3 | 256KB  |

| 1111         | 1111     | 1111 | 1111 | 1111:          | <br>0xFFFFF        |   | 200110 |

# **PROBLEM** 5 (15 PTS)

a) Perform the following additions and subtractions of the following unsigned integers. Use the fewest number of bits n to represent both operators. Indicate every carry (or borrow) from  $c_0$  to  $c_n$  (or  $b_0$  to  $b_n$ ). For the addition, determine whether there is an overflow. For the subtraction, determine whether we need to keep borrowing from a higher bit. (6 pts)  $\checkmark$  37 - 41

2

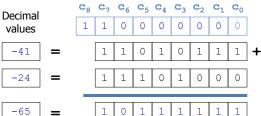

b) The figure shows two 8-bit operands represented in 2's complement. Perform the 8-bit addition operation, i.e., complete all the carries and the summation bits. Also, indicate the corresponding decimal numbers for the 8-bit operands and the 8-bit result.

Does this 8-bit operation incur in overflow? Value of the overflow bit:  $\frac{c_8 \oplus c_7 = 0}{c_8 = 1}$  Value of carry out bit:  $\frac{c_8 \oplus c_7 = 0}{c_8 = 1}$

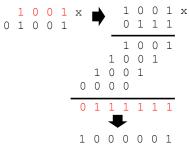

c) Perform binary multiplication of the following numbers that are represented in 2's complement arithmetic. (3 pts)

Yes

✓ 1001 x 01001

# **PROBLEM 6 (10 PTS)**

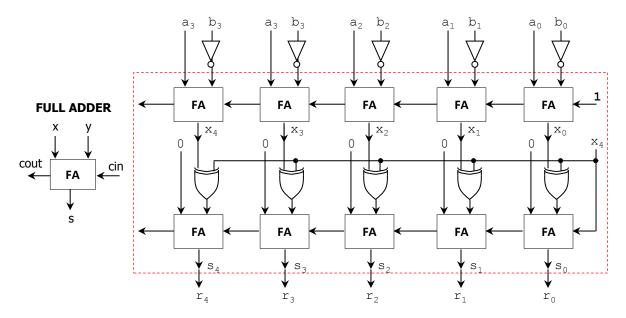

■ Sketch the circuit that computes |A - B|, where A, B are 4-bit <u>signed</u> numbers. For example,  $A = 0101, B = 1101 \rightarrow |A - B| = |5 - (-3)| = 8$ . You can only use full adders (or multi-bit adders) and logic gates. Your circuit must avoid overflow: design your circuit so that the result and intermediate operations have the proper number of bits.

$A = a_3 a_2 a_1 a_0$ ,  $B = b_3 b_2 b_1 b_0$

$A, B \in [-8,7] \rightarrow A, B$  require 4 bits in 2C representation.

- $\checkmark$   $X = A B \in [-15,15]$  requires 5 bits in 2C. Thus, we need to zero-extend A and B.

- $\checkmark$   $|X| = |A B| \in [0,15]$  requires 5 bits in 2C. Thus, the second operation  $0 \pm X$  only requires 5 bits.

- $If x_4 = 0 \rightarrow X \ge 0 \rightarrow \text{we do } 0 + X.$

- $\checkmark$   $R = |A B| \in [0,15]$  requires 5 bits in 2C. Note that the MSB is always 0.

3

# PROBLEM 7 (16 PTS)

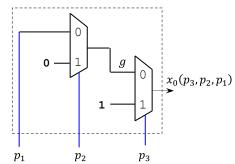

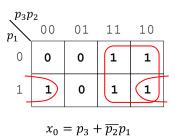

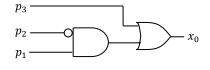

In a 4-to-2 priority encoder (like the one in Problem 2), it can be demonstrated that the output x<sub>0</sub> = p̄<sub>3</sub> p̄<sub>2</sub>p<sub>1</sub> + p<sub>3</sub>.

✓ Provide the simplified expression for x<sub>0</sub> and sketch this circuit using logic gates. (3 pts)

| p <sub>3</sub> | $p_2$ | $p_1$ | x <sub>0</sub> |

|----------------|-------|-------|----------------|

| 0              | 0     | 0     | 0              |

| 0              | 0     | 1     | 1              |

| 0              | 1     | 0     | 0              |

| 0              | 1     | 1     | 0              |

| 1              | 0     | 0     | 1              |

| 1              | 0     | 1     | 1              |

| 1              | 1     | 0     | 1              |

| 1              | 1     | 1     | 1              |

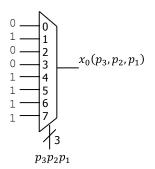

✓ Implement  $x_0$  using ONLY an 8-to-1 MUX. (3 pts).

✓ Implement  $x_0$  using ONLY 2-to-1 MUXs (AND, OR, NOT, XOR gates are not allowed) (10 pts).

$$\begin{split} x_0(p_3,p_2,p_1) &= p_3 + \overline{p_2}p_1 \\ x_0(p_3,p_2,p_1) &= \overline{p_3}x_0(0,p_2,p_1) + p_3x_0(1,p_2,p_1) = \overline{p_3}(\overline{p_2}p_1) + p_3(1) \\ x_0(p_3,p_2,p_1) &= \overline{p_3}g(p_2,p_1) + x_0(1) \\ g(p_2,p_1) &= \overline{p_2}g(0,p_1) + p_2g(1,p_1) = \overline{p_2}(p_1) + p_2(0) \end{split}$$